# A Vision for Modular, Ubiquitous & Scalable Compute Systems

Prepared by Johanna Swan, Intel Fellow & Director of Package Research & System Solutions

**Presented by Bernd Waidhas**

FTD | Technology Research | September 11, 2024

# Outline

- 1. Today's Domain Specific Systems & Trends

- Key thrusts to drive scale for high volume manufacturing

#### 2. Interconnect Scaling

- Solder vs. Hybrid Bonding

- Implications & Interactions

- Challenges & Opportunities

## 3. System Expansion & Connectivity

- Methods to Expand the Package

- Implications & Interactions

- Challenges & Opportunities

#### 4. Advanced Memory Integration

- Stacked vs. Side-by-Side on Interposer or Package

- Implications & Interactions

- Challenges & Opportunities

## 5. Summary

#### intel foundry 2

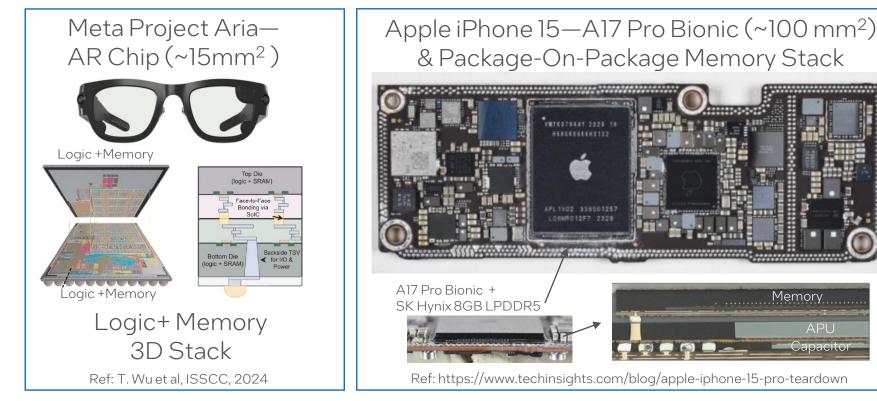

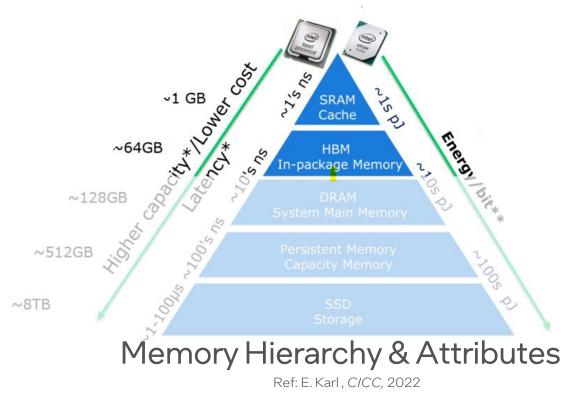

# Domain Specific Compute System Trends

Each market drives a specific form factor (size) and affordability target.

AI drives a need for more memory capacity and higher bandwidth with lower latency even for mobile products.

Intel Lunar Lake 3D with copackaged Memory (~740mm<sup>2</sup>)

Ref: Intel Newsroom

intel foundry

FTD | Technology Research | September 11, 2024

IEEE Electronics System-Integration Technology Conference—Keynote Berlin, Germany

Memory

# Domain Specific Compute System Trends (cont.)

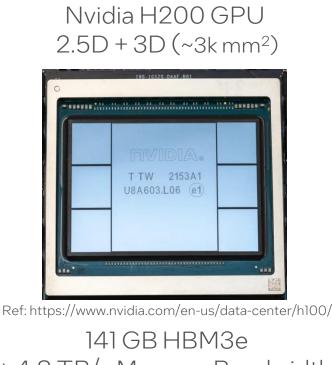

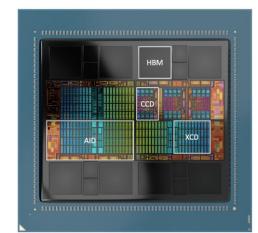

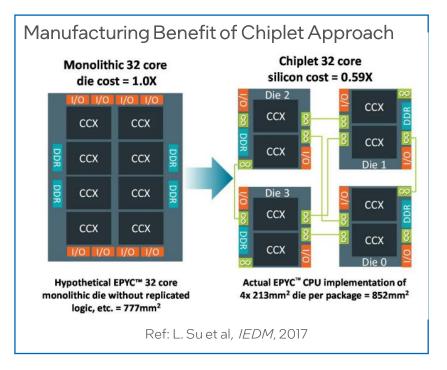

+ 4.8 TB/s Memory Bandwidth +NVLink 900GB/s +PCIe Gen 5: 128GB/s AMD MI300X Accelerator Modular 2.5D + 3D (~6k mm<sup>2</sup>)

Ref: A. Smith et al, ISSCC, 2024 192 GB HBM3e + 5.3 TB/s Memory Bandwidth + Infinity Fabric<sup>TM</sup> 896 GB/s +PCIe Gen5: 128 GB/s

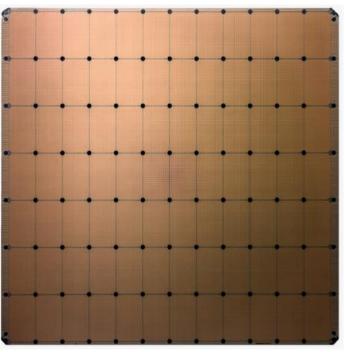

For high performance compute memory capacity & bandwidth as well as interconnect bandwidth are driving system architecture solutions

2.5 & 3D stacking is utilized yet still the package is growing in area

Modular chips with higher interconnect bandwidth are utilized to reduce cost

Cerebras Wafer Scale Engine (~46k mm<sup>2</sup>)

Ref: https://cerebras.ai/product-chip/

44GB on-chip memory + 21 PB/s Memory Bandwidth +214 PB/s Fabric Bandwidth

FTD | Technology Research | September 11, 2024

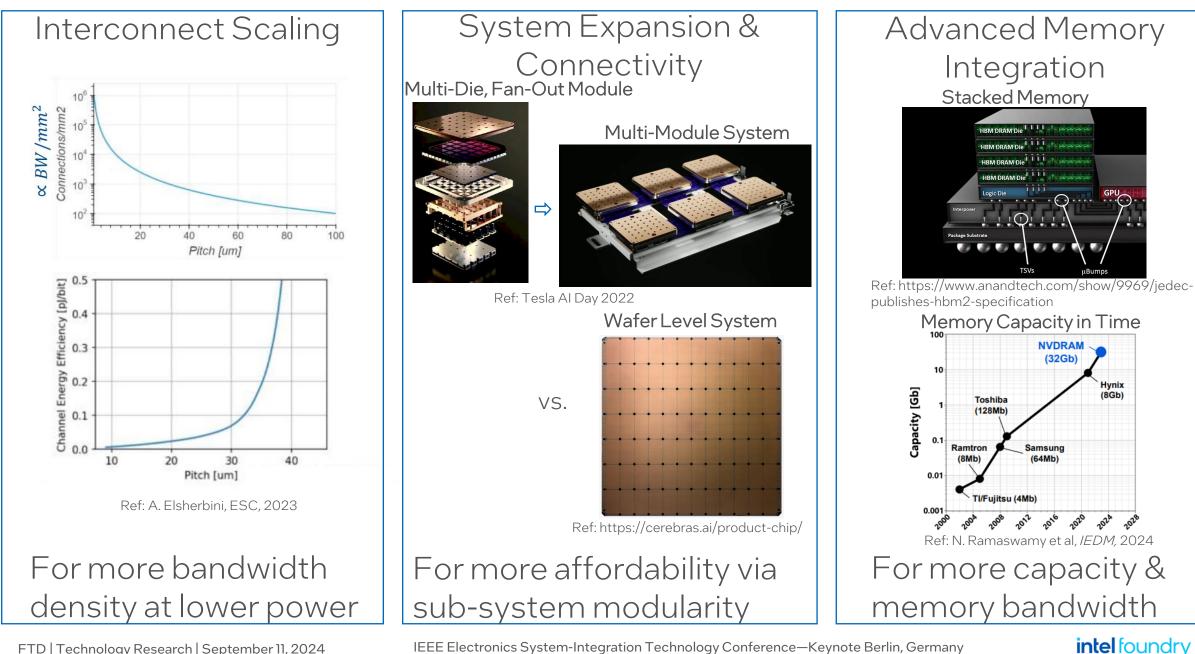

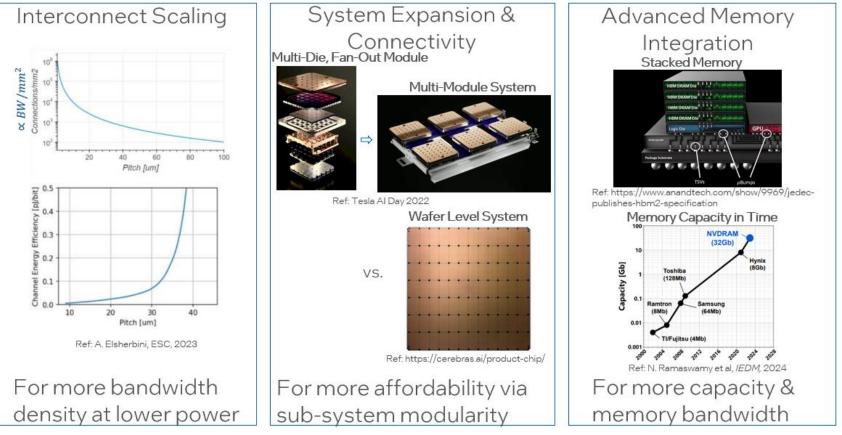

# 3 Key Thrusts are Evident

FTD | Technology Research | September 11, 2024

## Outline

#### Today's Domain Specific Systems & Trends Key thrusts to drive scale for high volume manufacturing

#### 2. Interconnect Scaling

- Solder vs. Hybrid Bonding

- Implications & Interactions

- Challenges & Opportunities

## 3. System Expansion & Connectivity

- Methods to Expand the Package

- Implications & Interactions

- Challenges & Opportunities

## 4. Advanced Memory Integration

- Stacked vs. Side-by-Side on Interposer or Package

- Implications & Interactions

- Challenges & Opportunities

## 5. Summary

#### intel foundry 6

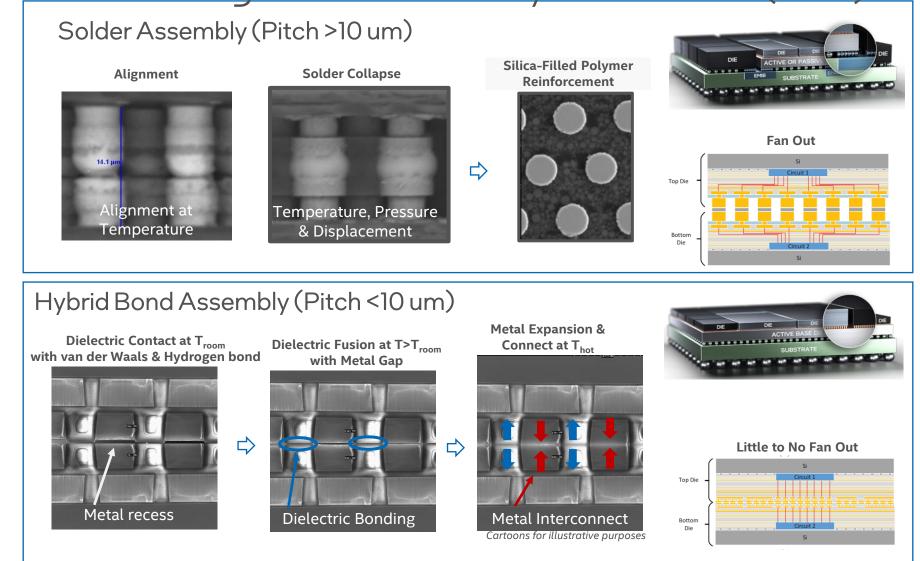

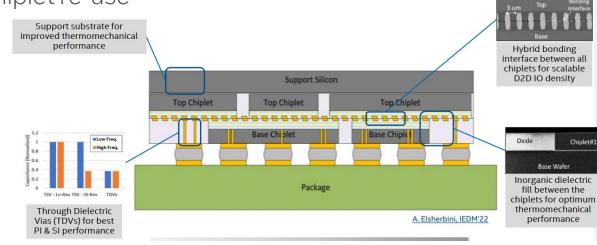

## Interconnect Scaling: Solder vs. Hybrid Bond (HBI) Assembly

Solder & Hybrid Bond Assembly may be utilized hierarchically to make composite packages.

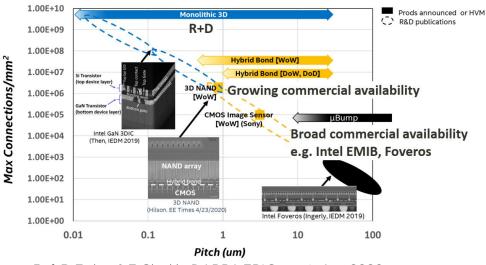

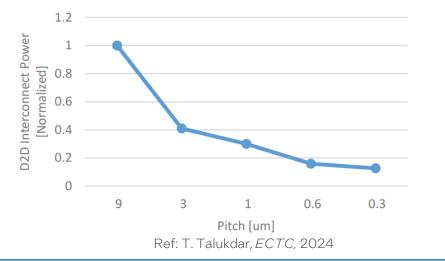

## Interconnect Scaling Implications & Interactions

Ref: P. Fisher & F. Sheikh, DARPA ERI Summit, Aug 2020

#### Die to Die Power Decreases With Pitch

Potential to enable assembled interconnect densities at >7M connections/mm<sup>2</sup>

Ref: T. Talukdar, ECTC, 2024

By utilizing quasi-monolithic integration features and materials may be selected for maximal performance & chiplet re-use

Ref: A. Elsherbini, ECS, 2023

FTD | Technology Research | September 11, 2024

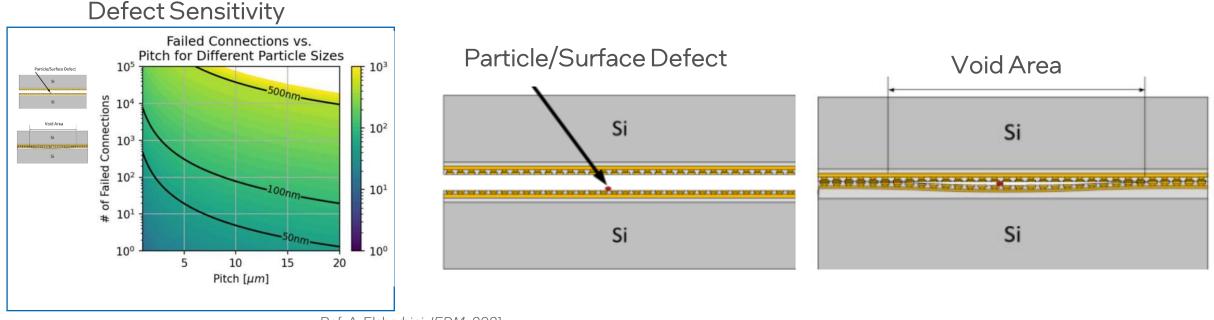

## Interconnect Challenges & Opportunities

Ref: A. Elsherbini, IEDM, 2021

Hybrid bonding drives significant cost to enable, i.e.

- Planarization

- Cleanliness

- Precision die placement

Opportunity: Lower-Cost, Pitch Scaled Assembly that is more defect tolerant.

FTD | Technology Research | September 11, 2024

IEEE Electronics System-Integration Technology Conference—Keynote Berlin, Germany

#### intel foundry

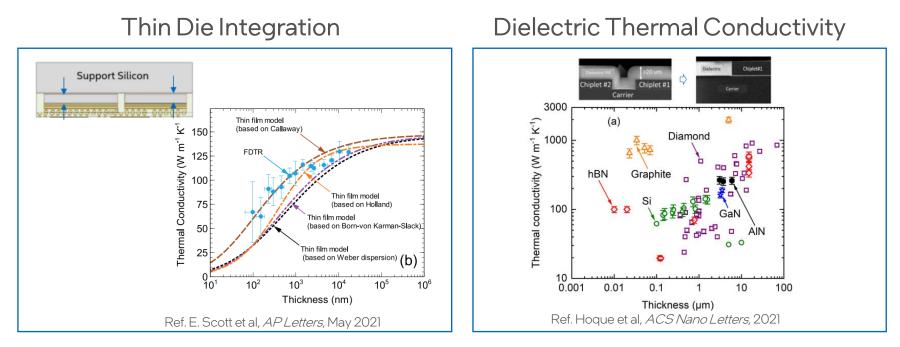

## Interconnect Challenges & Opportunities

Today's systems rely on thin die for stacked integration and encapsulated with SiO<sub>2</sub>

- Thermal Conductivity decays when silicon thickness < 10 um

- Dielectric Constant ~3.9

- Thermal Conductivity ~1.3 W/mK

Opportunity: Enable higher thermal conductivity integration schemes with low dielectric constant materials

FTD | Technology Research | September 11, 2024

IEEE Electronics System-Integration Technology Conference—Keynote Berlin, Germany

#### intel foundry <sup>10</sup>

# Outline

Today's Domain Specific Systems & Trends

Key thrusts to drive scale for high volume manufacturing

#### 2. Interconnect Scaling

- Solder vs. Hybrid Bonding

- Implications & Interactions

- Challenges & Opportunities

## 3. System Expansion & Connectivity

- Methods to Expand the Package

- Implications & Interactions

- Challenges & Opportunities

## 4. Advanced Memory Integration

- Stacked vs. Side-by-Side on Interposer or Package

- Implications & Interactions

- Challenges & Opportunities

## 5. Summary

#### intel foundry <sup>11</sup>

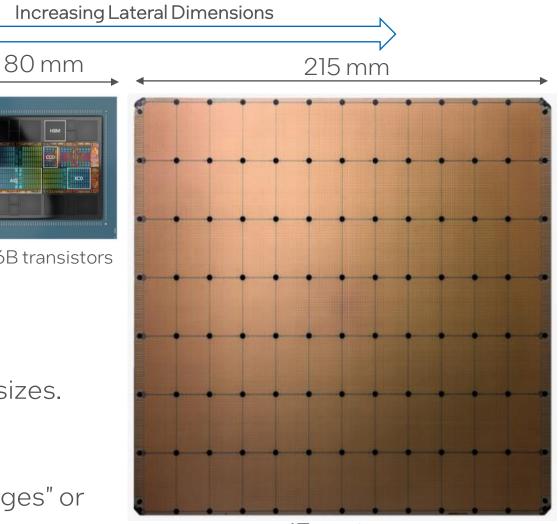

## Systems are Expanding in Dimension

80B transistors

146B transistors

Al is driving system expansion and with it the package sizes.

Solutions include either

- Transition from Wafer to Panel level fan out "packages" or

- Modular connectorized systems across large areas

Methods to Expand the System (Not the Package)

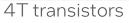

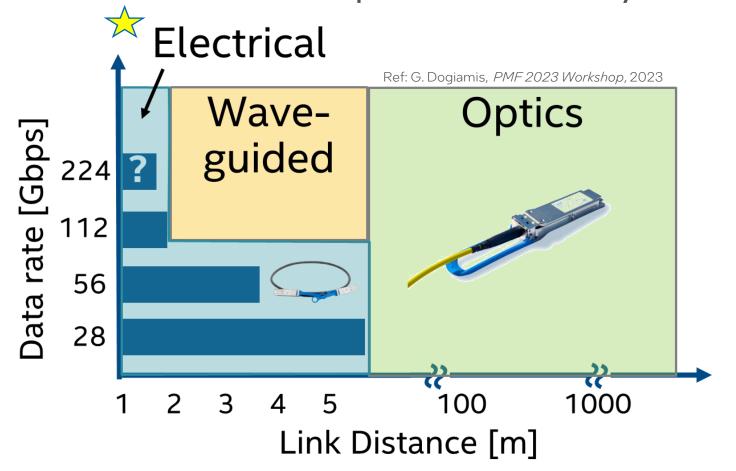

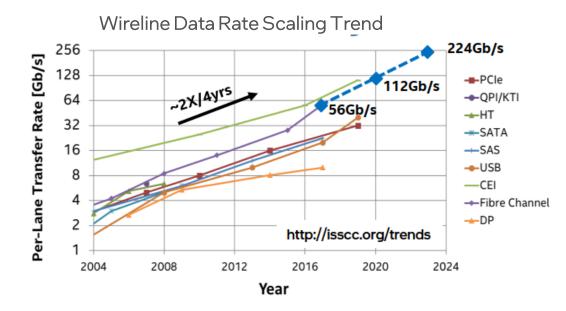

As data rates increase—the reach may be penalized by power and cost overheads.

System co-optimization for bandwidth, power efficiency, bit error rate, physical fit and cost provide a means to modularize solutions

**Connector Solutions**

**Electrical Top Side Connector Solutions**

Motherboard

Flex

CPU

High-speed

connector

Socket

CPU

Ref: S. Fathololoumi et al, Hot Chips, 2024

13

intel foundry

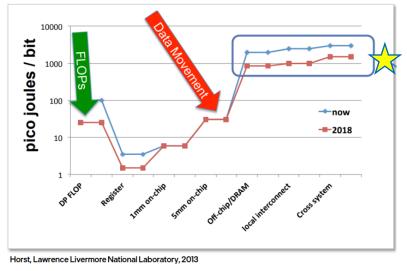

# System Expansion Challenges & Opportunities

System Expansion Via Multiple Interconnected Packages

Challenges:

- Shoreline restrictions limiting fit & on-to-off package transition

- Data rate scaling with power efficiency improvements

- Extremely low loss, reworkable, cost-affordable connectors

Opportunity: to modularize packages for affordability

Data Movement Power Efficiency Trend

Ref: E. Karl , C/CC, 2022

FTD | Technology Research | September 11, 2024

# Outline

Today's Domain Specific Systems & Trends

Key thrusts to drive scale for high volume manufacturing

#### 2. Interconnect Scaling

- Solder vs. Hybrid Bonding

- Implications & Interactions

- Challenges & Opportunities

## 3. System Expansion & Connectivity

- Methods to Expand the Package

- Implications & Interactions

- Challenges & Opportunities

## 4. Advanced Memory Integration

- Stacked vs. Side-by-Side on Interposer or Package

- Implications & Interactions

- Challenges & Opportunities

## 5. Summary

#### intel foundry <sup>15</sup>

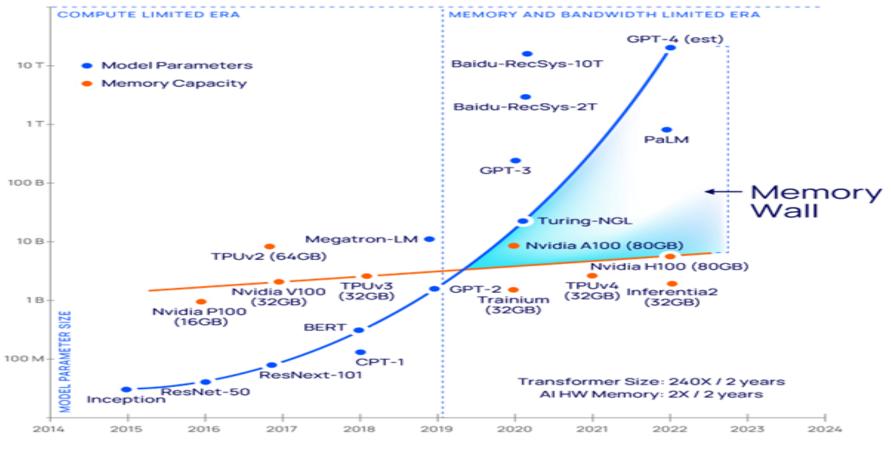

## Memory Integration is even more challenging for AI LLM

AI compute and memory demands are growing exponentially. [Training Compute-Optimal LLMs (Mar '22), Celestial.ai]

Today memory capacity & interconnect bandwidth limit AI Large Language Models

FTD | Technology Research | September 11, 2024

IEEE Electronics System-Integration Technology Conference—Keynote Berlin, Germany

#### intel foundry <sup>16</sup>

## Memory Integration Key Challenge

More memory capacity & bandwidth is needed, driving

- In/Near Memory Compute Advancements and/or

- More in-package memory with hierarchical caching & higher density interconnects

#### intel foundry <sup>17</sup>

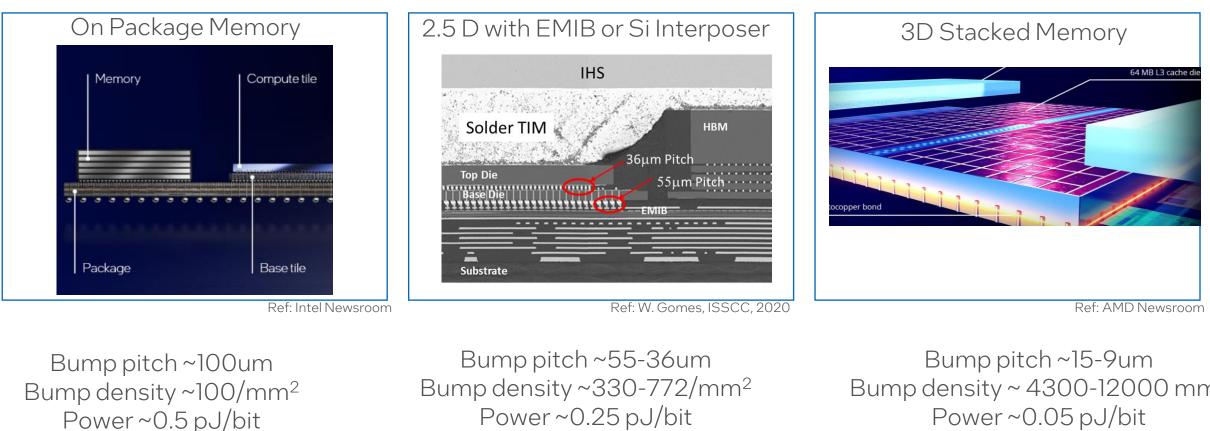

## Memory Implementations Today

Memory soldered to package Normalized latency

Power~0.25 pJ/bit

Bump density ~ 4300-12000 mm<sup>2</sup> Power ~0.05 pJ/bit

Memory soldered to passive silicon Relatively Lower latency

Cache stacked Hybrid Bond ~8x lower latency than 55um

#### Demand for memory stacking is at an all time high

FTD | Technology Research | September 11, 2024

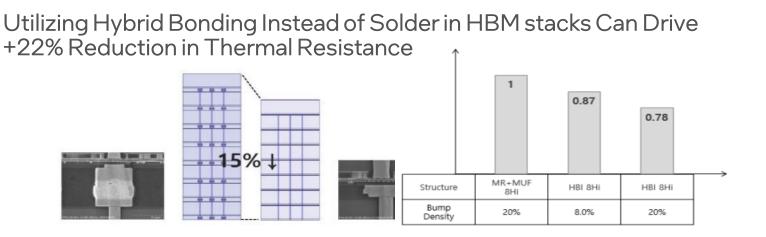

## Memory Integration Key Challenge Thermal Management

Ref: K. Kim et al, *ECTC,* 2023

Thermal management is a challenge, despite hybrid bond assembly providing a thermal conductivity advantage.

- Memory on logic translates to even higher power density

- Tighter coupling leads to more thermal cross-talk

- Available thermal dissipative power (TDP) is relatively fixed per form factor

Opportunities: Unified control of both processor and memory power in logic to memory stack & disruptive TDP enablers.

## Summary

From augmented reality to high performance compute, there is a demand for more memory capacity and higher interconnect bandwidth with lower latency.

- Technology which can be modularized and scaled out enables affordable, ubiquitous compute system solutions

- Three key vectors for addressing this vision of modularized solutions include: a) interconnect scaling, b) system expansion & connectivity, and c) advanced memory integration

- For each market, co-optimization across these thrusts are needed to meet the form factor & performance target.

FTD | Technology Research | September 11, 2024

#

All product and service plans, and roadmaps are subject to change without notice. Any forecasts of products, services or technologies needed for Intel's operations are provided for discussion purposes only. Intel will have no liability to make any purchase in connection with forecasts published in this document. Code names are often used by Intel to identify products, services or technologies that are in development and usage may change over time. Product, service and technology performance varies by use, configuration and other factors. No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document. Learn more at <u>www.Intel.com/PerformanceIndex</u> and <u>www.Intel.com/ProcessInnovation</u>.

Reference to research results, including comparisons to products, services or technology performance are estimates and do not imply availability. The products and services described may contain defects or errors which may cause deviation from published specifications. Current characterized errata are available on request. Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade. Statements in this document that refer to future plans or expectations are forward-looking statements. These statements are based on current expectations and involve many risks and uncertainties that could cause actual results to differ materially from those expressed or implied in such statements. For more information on the factors that could cause actual results to differ materially, see our most recent earnings releases, annual report on form 10-K and other SEC filings at <u>www.intc.com</u>.

© Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others. This document contains information on products and technologies in development.